来源:科创板日报

超威(AMD)CEO苏姿丰今日(6月1日)表示,AMD已与台积电紧密合作,开发出领先业界的3D chiplet(小芯片/芯片粒/裸芯片)技术,今年底前开始生产运用3D chiplet技术的未来高阶运算(HPC)产品。

据了解,AMD已向台积电预订明、后两年5纳米及3纳米产能,预计2022年推出5纳米Zen4架构处理器,2023-2024年间将推出3纳米Zen5架构处理器,届时将成为台积电5纳米及3纳米高效能运算产品的最大客户。

AMD引领chiplet风潮

Chiplet是先进封装技术的一种,指将大尺寸的多核心的设计分散到较小的小芯片。它并非全新的概念,早在2014/2015年就有Fabless业者提出相似的设计架构。

其提出背景在于,后摩尔时代,半导体先进制程不断往7nm/5nm甚至以下迈进,晶片设计与制造工艺微缩的难度、成本与开发时间均呈现跳跃式的增长。而通过chiplet架构与先进封装的高密度互联,能实现以更低成本提供相同等级效能表现。

在这样的思路下,chiplet设计渐成主流,包括Hisilicon、Marvell、Xilinx、AMD到Intel在内的Fabless与IDM大厂皆积极推动chiplet生态的发展。

AMD无疑为这波chiplet风潮的引领者。

该公司从2019年起全面采用chiplet技术,彼时苏姿丰便表示,AMD仍会与台积电等晶圆代工厂合作持续进行制程微缩,摩尔定律仍然有效,只是推进的速度明显变慢。要在制程微缩时获得效能提升,可以通过创新芯片架构、异质整合平台、chiplet系统级封装等创新方法来达到目标。

目前,AMD已经建构了自己的chiplet生态系统,生产了Ryzen和Epycx86处理器。

本土半导体板块迎来加速追赶黄金期

对于国内半导体企业来说,抓住这些先进封装技术至关重要。

5月14日,国家科技体制改革和创新体系建设领导小组第十八次会议在北京召开。会议讨论了面向后摩尔时代的集成电路潜在颠覆性技术。

对此,天风证券分析师潘暕认为,后摩尔时代来临,本土半导体板块迎来加速追赶黄金期,先进封装具有潜在颠覆性,预计2025市场可达430亿美元。

Yole预测先进封装在2019年到2025年之间预期将以7%的CAGR增长,到2025年规模可达430亿美元。2018到2020年三年中,我国先进封装占封测业比重分别为35%、37%和40%左右,预计到2022年后先进封装的产品占比将超过45%。

另外,和chiplet一样,系统级封装(SiP)也具备研发周期短、节省空间的优势。

《科创板日报》梳理相关公司:

国内已在先进封装领域有长足发展的企业包括长电科技、通富微电、晶方科技、华天科技等。

其中,通富微电深度绑定AMD,通富超威苏州和通富超威槟城两个子公司先进封装产品占比100%,包括FCBGA、FCPGA、FCLGA以及MCM等高端封装技术;

华天科技已自主研发出达到国际先进水平的多芯片封装(MCP)技术、多芯片堆叠(3D)封装技术、薄型高密度集成电路技术、集成电路封装防离层技术、16nm晶圆级凸点技术、基于C2W和TSV的声表面滤波器封装技术等先进封装技术;

长电科技在先进封装技术覆盖度上与全球第一的日月光集团旗鼓相当,具备行业领先的SiP、WLCSP、FC、eWLB、PiP、PoP及2.5/3D等高端封装技术;

晶方科技是光学赛道TSV-CIS封测龙头,具备8英寸、12英寸晶圆级芯片尺寸封装技术规模量产封装线,涵盖晶圆级到芯片级的一站式综合封装服务能力。

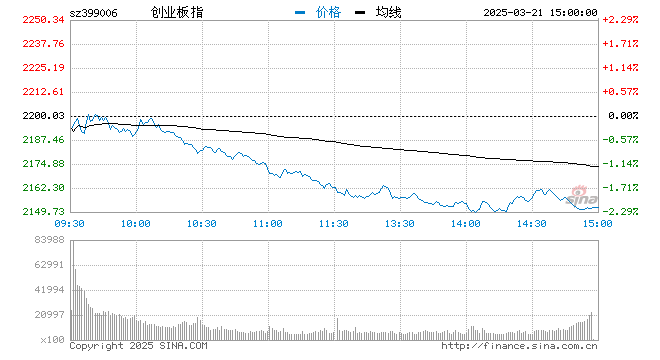

牛市来了?如何快速上车,金牌投顾服务免费送>>